# Project 1 - AC to DC

Full Name: Yousif Fadhel

Student Number: 400434747

Mac ID: fadhely

Date: February 10, 2025

# Summary

While high-voltage alternating-current (AC) power lights up our homes and cities, the heartbeat of modern technology, from cutting-edge electric vehicles and renewable energy systems to life-saving medical devices typically run on low-voltage direct-current (DC) power. This project focused on designing a rectifier and filter system to convert a 120 V, 1 kHz AC input into a stable DC output of 10 mA at 3 V, with a tolerance of ±0.1 V, suitable for powering sensitive electronics.

# **Design Approach & Specifications**

### 1. Transformer:

Transformers are imperative in the process of converting a given AC signal into a DC output. The transformer would reduce the 120V rms input to a more manageable voltage. The transformer is able to achieve this through a coil ratio. In the circuit analysis of the rectifier depicted later in this report, it was determined that an AC input with an amplitude of 4.6 V was required. Therefore, to step down 120 V RMS to a *v*o with an amplitude of 4.6 V approximately 37 input coils will correspond to 1 output coil, stepping down the voltage from 120 V to around 4.6 V. In my design, this stepped-down voltage of 4.6 V will serve as the input to the rectifier, ensuring the system is ready for the next stage of conversion.

Calculation to determine coil ratio:

$$\frac{120 \ V \times \sqrt{2}}{4.6 \ V} = \frac{N_1}{N_2} \cong \frac{37}{1}$$

### 2. Rectifier:

The chosen rectifier topology for this project was the full-wave bridge rectifier. This type of rectifier converts an alternating current (AC) input into a pulsating direct current (DC) output by allowing current to flow in the same direction through the load during both halves of the AC cycle. This selection was made over the center-tapped full-wave rectifier and the half-wave rectifier. Both the full wave bridge rectifier and the center-tapped full wave rectifier are superior to the half-wave rectifier as they make use of the negative half of the input sine wave voltage through inverting it, resulting in a DC output. The half-wave rectifier is designed to neglect the negative portion of the wave resulting in a pulsated DC wave which is much less efficient. However, what makes the bridge rectifier a better selection than the center-tapped rectifier is that it is much more resource-efficient, requiring half as many coils within its secondary winding as

its counterpart. This rectifier is composed of 4 diodes, each pair in series with another and bridged together by a load resistor. The diodes being used are the 1N4148 which have a voltage drop of 0.7 volts and a voltage breakdown at 100 volts.

# 3. Filter:

The filter is the final component of my design where the voltage would pass through to result in a DC voltage. This was performed by adding a capacitor in series with the load resistor using the output of the rectifier as its input. The purpose of this setup is to assist in reducing any ripples and or fluctuations of the voltage. In my design, I incorporated a  $100\mu$ F capacitor to significantly reduce voltage ripple. The capacitor achieves this by absorbing or releasing voltage as needed, ensuring that the output across the load resistor more closely resembles a stable DC signal.

## 4. Regulator:

Voltage regulators, such as a zener diode, are used to maintain a constant and stable output voltage level despite variations in input voltage or load conditions. Regulators ensure that electronic devices receive a consistent voltage, which is crucial for their proper operation and longevity. For this design, longevity is a non-factor and the output voltage was safely within the acceptable range, a regulator was deemed unnecessary, and not implemented into the design.

## 5. Circuit Schematic

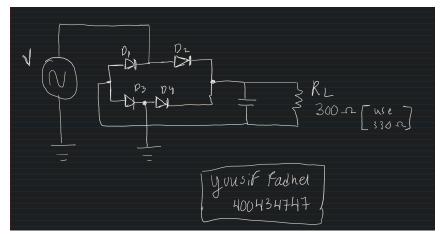

Initial Drawn Circuit Schematic

# 6. Calculations:

Full WAVE BAIOGIE RECITIFIER:

given: we want

$$V_0 = 3V$$

$\Rightarrow V_0 = V_{in} - 2 (Doole Voltage Orap) - 0.2V$

$\Rightarrow 3 + 2(0.7) + 0.2 = V_{in}$

$\therefore V_{in} = 4.6 Volta$

LOAD RESISTOR:  $V = IR$ ,  $R = V/I$

$R = \frac{3V}{0.01A} = 300 - RL$

Transformer  $\Rightarrow V_0 = 4.6V$

$a = \frac{V primary}{V secondary} = 120 rms \times \sqrt{2} \frac{amplitude}{Cms} \approx \frac{37}{1}$

Filter Calculation:

$\cdot reduce the voltage$

$V_{rpp} = \frac{Iout}{f.C} = \frac{10 mA}{(2.1000Hz)(100.10^9)} = 0.05V$

- When using a full wave bridge rectifier, the frequency is doubled

- The lowest V*ripple* is ideal thus a great amount of capacitance is needed.

- The largest capacitor available for use in this project is  $100\mu F$

- In theory, this design should produce a 3 V output with a ripple of 0.05 V

## 7. Design Tradeoffs

In most designs, trade-offs are inevitable, and this project is no exception. One of the primary safety considerations in this design is the use of 1N4148 diodes in the full-wave bridge rectifier. According to the diode datasheet, the forward voltage drop can vary significantly, reaching up to 1 volt under certain conditions, compared to the typical assumed value of 0.7 V. This variance could impact the resistor calculations and, consequently, alter the output voltage or current, potentially affecting the stability and safety of the circuit. To mitigate this, careful selection and testing of components are essential to ensure the circuit operates within safe limits.

Another safety-related trade-off is the use of a full-wave bridge rectifier instead of a center-tapped design. While the bridge rectifier allows for the use of a single power source and maximizes the utilization of available diodes, it introduces additional diode losses and heat dissipation, which could pose safety risks if not properly managed. Ensuring adequate heat dissipation and using resistors with appropriate power ratings are critical to maintaining safe operating conditions. Furthermore, despite the advantages mentioned previously regarding the selection of the full-wave bridge rectifier, it does require 4 diodes in comparison to 2 diodes for the other full-wave option and only 1 for the half-wave rectifier.

# Measurements & Analysis

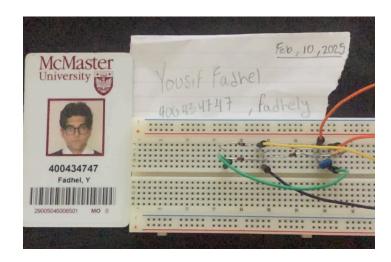

1. Photograph of Circuit

In the above photo, the circuit has been constructed following the circuit schematic. The orange wires are the probes measuring the voltage across the 330-ohm load resistor, the yellow

wire is the wave generator, the green wire is a short circuit connection and the black wire is ground.

## 2. Measurement Procedure

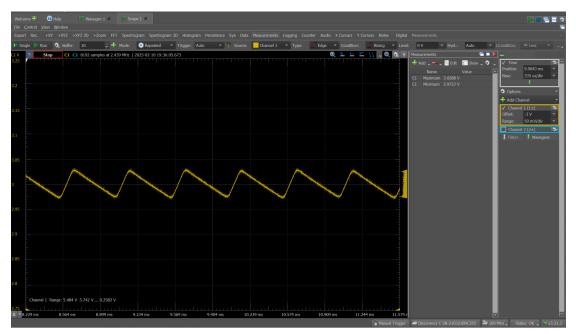

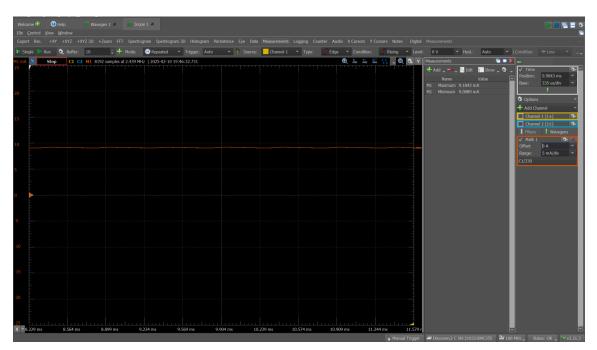

Determining the performance of the designed full wave bridge rectifier was conducted by measuring the load voltage across the load resistor and displaying the value alongside its waveform on the AD2 Oscilloscope. In order for an effective output to be displayed several troubleshooting steps had to be implemented and will be discussed in further detail in the discussion section of the report. Important things to note are that the input voltages had to be increased from the ideal 2.3 V to 2.5 V resulting in a net input of 5 V and in place of the ground wire the second channel of the oscilloscope was used as well. The oscilloscope displayed a DC output of 3 V with a slight ripple that fell within the  $\pm 0.1$  V specification. Additionally, the current graph was also plotted through the implementation of a Math channel on the WaveForms software that applied the formula C1 / 330, essentially dividing the load voltage by the load resistor. The value calculated and depicted was only marginally off the desired 10 mA hovering around 9 mA.

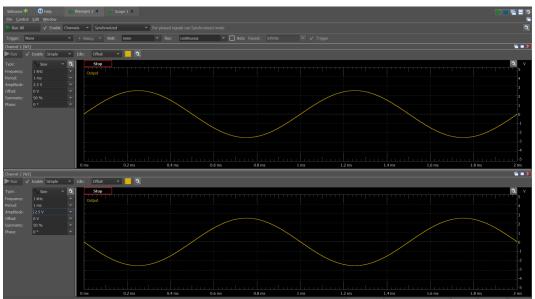

## 3. Oscilloscope Input Settings & Output Waveforms

Synchronized Channels Producing a 5V Input

The output voltage from the oscilloscope. The measurement channels on the right-hand side depict the max and min voltages nearing the desired values, thus verifying the design.

The output current at approximately 9 mA is visualized on the oscilloscope and seen numerically on the measurement channels.

# Simulation

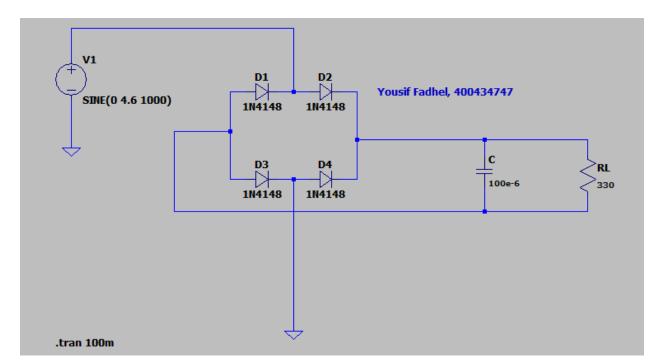

1. Circuit Schematic from LTspice:

2. Netlist:

```

* C:\Users\yousi\Documents\LTspice\Draft1.asc

C N003 N002 100e-6

RL N003 N002 330

V1 N001 0 SINE(0 4.6 1000)

D1 N002 N001 1N4148

D2 N001 N003 1N4148

D3 N002 0 1N4148

D4 0 N003 1N4148

.model D D

.lib C:\Users\yousi\AppData\Local\LTspice\lib\cmp\standard.dio

* Yousif Fadhel, 400434747

.tran 100m

.backanno

.end

```

### 3. Simulation Conditions & Outputs:

The LTspice simulation was specified to run as a transient simulation for a 100 ms time interval.

| 3.3V           |           |                              |      | V(N003,N002) |      |      |      |                   |      |

|----------------|-----------|------------------------------|------|--------------|------|------|------|-------------------|------|

| 3.0V-<br>2.7V- |           |                              |      |              |      |      |      |                   |      |

| 2.4V-          |           |                              |      |              |      |      |      |                   |      |

| 2.1V-          |           |                              |      |              |      |      |      |                   |      |

| 1.8V-<br>1.5V- |           |                              |      |              |      |      |      |                   |      |

| 1.2V-          |           |                              |      |              |      |      |      |                   |      |

| 0.9V-<br>0.6V- |           |                              |      |              |      |      |      |                   |      |

| 0.3V-          |           |                              |      |              |      |      |      |                   |      |

| 0.0V           |           |                              |      |              |      |      |      |                   |      |

| 0.0V-+<br>Oms  | 10ms 20ms | 30ms                         | 40ms | 50ms         | 60ms | 70ms | 80ms | 90ms              | 100m |

|                | 10ms 20ms | <sup>30ms</sup><br>003,N002) | 40ms | 50ms         | 60ms | 70ms | 80ms | 90 <sup>m</sup> s | 100n |

|                | V(N       | 003,N002)                    |      |              |      |      |      | 90ms              | 100m |

|                |           | 003,N002)                    |      |              |      |      |      | 30ms              | 100m |

|                | V(N       | 003,N002)                    |      |              |      |      |      | 30ms              | 100m |

| 🗗 Dr                       | aft1.raw          |        | ×          |  |  |

|----------------------------|-------------------|--------|------------|--|--|

| - Cursor 1<br>V(N003,N002) |                   |        |            |  |  |

| Horz:                      | 44.294547ms       | Vert:  | 3.0076746V |  |  |

| Cursor                     | 2                 |        |            |  |  |

| Horz:                      | N/A               | Vert   | N/A        |  |  |

| Diff (Cu                   | ursor2 - Cursor1) |        |            |  |  |

| Horz:                      | N/A               | Vert   | N/A        |  |  |

| Freq:                      | N/A               | Slope: | N/A        |  |  |

|                            |                   |        |            |  |  |

|                            |                   |        |            |  |  |

|                            |                   |        |            |  |  |

|                            |                   |        |            |  |  |

|                            | 50ms              |        | 60ms       |  |  |

The voltage drop across the load resistor, simulated on LTspice

|             |                       |        |             | I(RL) |  |

|-------------|-----------------------|--------|-------------|-------|--|

|             |                       |        |             |       |  |

| mannananana |                       | sesses | nononononon |       |  |

|             |                       |        |             |       |  |

|             |                       |        |             |       |  |

| 1           | Draft1.raw            |        | ×           |       |  |

| Cu          | rsor 1                |        |             |       |  |

|             | I(RL)                 |        |             |       |  |

| Hor         | z: 31.182796ms        | Vert:  | 9.023698mA  |       |  |

| - Cu        | rsor 2                |        |             |       |  |

|             |                       | _      |             |       |  |

| Hor         | rz: N/A               | Vert:  | N/A         |       |  |

| — Dif       | f (Cursor2 - Cursor1) |        |             |       |  |

| Hor         | rz: N/A               | Vert:  | N/A         |       |  |

| Fre         | q: N/A                | Slope: | N/A         |       |  |

|             | · ·                   | -      |             |       |  |

|             |                       |        |             |       |  |

|             |                       |        |             |       |  |

|             |                       |        |             |       |  |

|             |                       |        |             |       |  |

|             |                       |        |             |       |  |

|             |                       |        |             |       |  |

| 30ms        | 40                    | )ms    |             | 50ms  |  |

The output current, simulated on LTspice

# Discussion

## 1. Results

The LTspice simulation results demonstrate the ideal performance of the proposed design, effectively showcasing its ability to step down 120V RMS to a voltage within the desired range of 2.9 to 3.1 volts under perfect conditions. However, real-world implementation introduces various discrepancies and factors that can impact the circuit's performance. These include potential issues such as faulty wiring, incorrect component or pin connections, and inaccuracies in scope readings. Despite these challenges, the actual measurements taken with the AD2 indicate that the circuit operates within an acceptable range, aligning reasonably well with the simulation results.

## 2. Limitations & Discrepancies

The limitations associated with this project are heavily correlated to the components used. To scale the voltage or current output, it would not be wise to use the same resistor due to its inherently low dissipation capacity which could result in major safety concerns and resistor burnouts. Additionally, there are times when it would be beneficial to increase the voltage supply however due to the limitations of the AD2 this was not possible to a meaningful point which is also the reason there was a 0.2 V error management added to the calculation. Other discrepancies may be due to potential internal resistance within the AD2, using 2 sources to simulate a single source, and having to increase the input voltage to produce the desired output due to the clipping behavior that was mentioned previously.

## 3. Troubleshooting

In terms of troubleshooting, the majority of the issues were associated with getting the desired output on the WaveForms application. After having built the circuit according to the simulated schematic it was evident that the resulting graph was incorrect and the Max and Min values were completely wrong. To troubleshoot this issue, the voltages of individual components were measured to verify the voltage drops were equivalent to the assumed values. Specifically, the diodes had notable discrepancies and it became clear that clipping was prevalent. Clipping behavior was observed when the voltage exceeded the circuit's capacity, leading to a flattened or distorted output waveform. This issue was resolved by adjusting the source voltages to ensure the output remained within the desired range. The only way to appropriately do this given the limitations of the software was to introduce a second source and apply the sine waves synchronously.